Webinar

A Dive into DDR5: An Engineers Guide to Simulating and Validating the Latest Generation of DDR

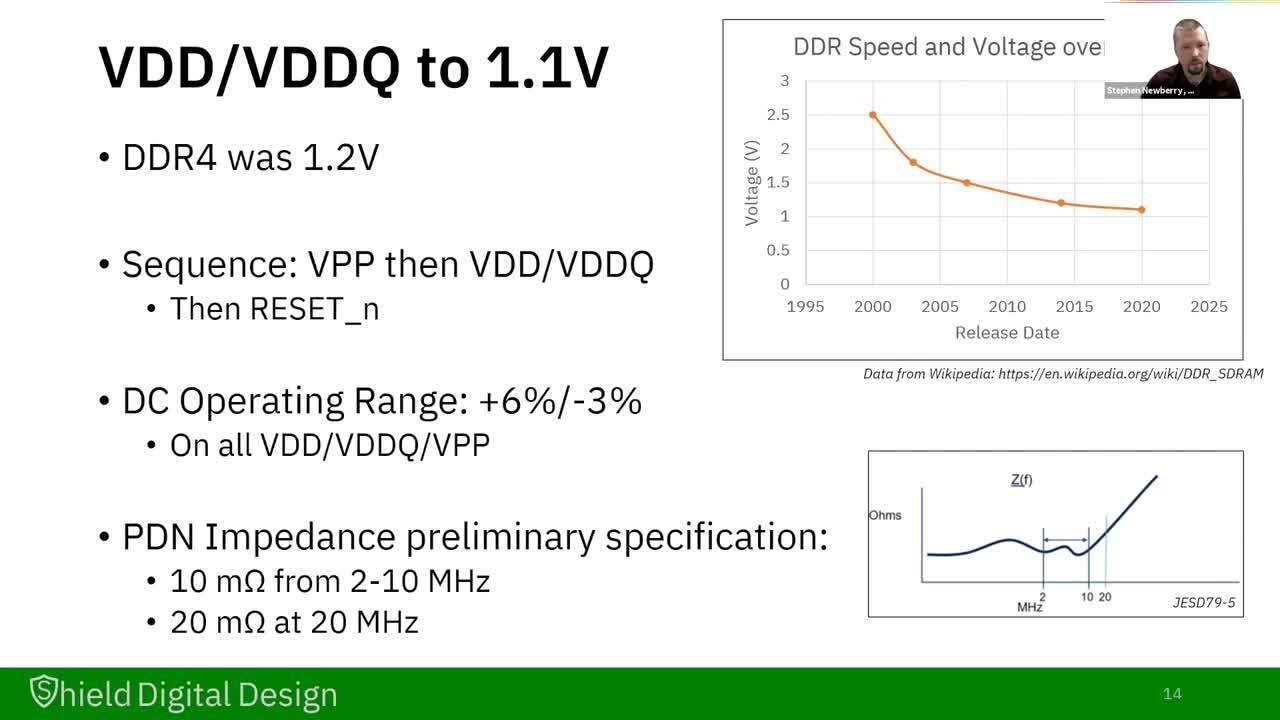

DDR5 represents a significant performance improvement to the DDR interface over DDR4 with data transfer rates going from 3200 MT/s to as much as 8400 MT/s according to the JEDEC spec. With this increased performance comes architectural changes that must be understood to effectively design and leverage these next generation memory devices. These changes also require updated simulation techniques and methodologies to ensure accurate and effective characterization of the DDR5 interface. Join us to learn from an industry professional how to upgrade your designs with DDR5 and simulate for success.

What you will learn:

- Overview of latest DDR5 changes vs DDR4

- Enhancements and new features in DDR5

- How these changes such as decision feedback equalization (DFE) impact simulation and analysis

- How to effectively simulate and qualify DDR5 interfaces with Sigrity

Want to Learn More About DDR5 Before this Session? Checkout Stephens Recent CadenceLive Session on whats New and Different with DDR5

About your Presenter

Stephen Newberry

Stephen is a Signal Integrity Engineer at Astranis with a B.S. in ECE from Rutgers. Along with being a father of four, he is the founder of Shield Digital Design. Shield Digital Design is a Signal Integrity and Power Integrity contracting firm handling pre-layout constraints, layout guidance, and post-layout validation.

Copyright EMA Design Automation, Inc

https://www.ema-eda.com/